A VHDL Code for Offset Pulse Position Modulation Working with Reed Solomon System by Using ModelSim

DOI:

https://doi.org/10.51173/jt.v4i4.758Keywords:

VHDL, ECC, FPGA, RS, OPPM, ModelSimAbstract

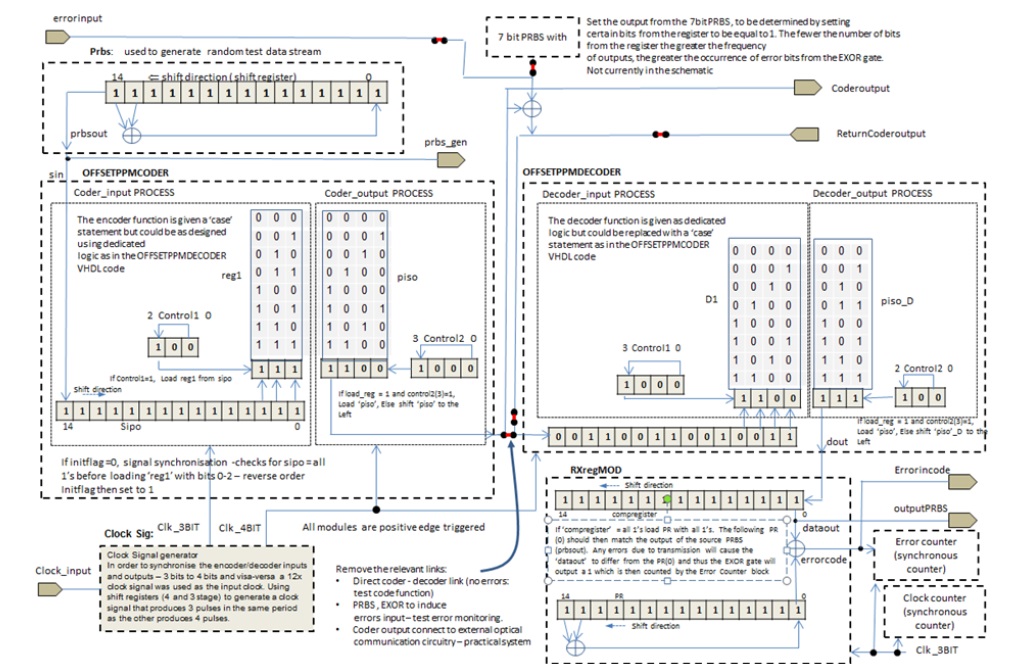

Error correction codes, often known as ECC, play a significant part in the process of detecting and correcting data mistakes that occur through communication channels that are unreliable or noisy. The essential concept behind error correction through ECC is to supplement the message that is being sent by the transmitter with redundant bits, the values of which are determined by the parameters n and k. These bits can then be utilized by the receiver to identify and correct specific types of errors. ECC is utilized in a wide variety of applications, including but not limited to data storage, the Internet, and telecommunications. There are numerous variations of ECC, including linear block, convolutional, and turbo codes, among others. The results of a simulation of a linear block reed Solomon, for example, with offset pulse position modulation have been presented in this study. The simulation was carried out in very high-speed integrated circuit hardware description language (VHDL), and a field-programmable gate array was used (FPGA) It made use of a Boolean function to function to program code for an algorithm that is working. Because of its performance, time to market, cost, reliability, and long-term maintenance benefits, FPGA is an appropriate platform for implementing error correction code (ECC). As a part of this project, the technique of offset Pulse Position Modulation (Offset PPM) was invented as an outstanding solution to code the fiber-optic applications and Reed Solomon (RS) codes apply to ModelSim SE-64 10.5 software. In addition, this coding scheme has been approved by the simulation and is matched with theory, and it is expected to be implemented shortly. The study begins with a concise introduction to RS encode/decode about design and performance and then moves on to discuss the development result of simulation and hardware implementation.

Downloads

References

Sibley, M.J., Analysis of offset pulse position modulation-a novel reduced bandwidth coding scheme. IET optoelectronics, 2011. 5(4): p. 144-150.

Soro, A. and J. Lacan. FNT-based Reed-Solomon erasure codes. in 2010 7th IEEE Consumer Communications and Networking Conference. 2010. IEEE.

Chou, C.-J., S. Mohanakrishnan, and J.B. Evans. FPGA implementation of digital filters. in Proc. Icspat. 1993. Citeseer.

Chandrasetty, V.A., and S.M. Aziz, FPGA Implementation of a LDPC Decoder using a Reduced Complexity Message Passing Algorithm. J. Networks, 2011. 6(1): p. 36-45.

Almeida, G.M., et al. A Reed-Solomon algorithm for FPGA area optimization in space applications. in Second NASA/ESA Conference on Adaptive Hardware and Systems (AHS 2007). 2007. IEEE.

Gao, Z., et al., Design of FPGA-Implemented Reed–Solomon Erasure Code (RS-EC) Decoders With Fault Detection and Location on User Memory. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2021. 29(6): p. 1073-1082.

Dinh, T. X., Nguyen, L. Y. N., Mohan, L. J., Boztas, S., Luong, T. T., & Dau, S. H. (2022). Practical Considerations in Repairing Reed-Solomon Codes. arXiv preprint arXiv:2205.11015.

Hormann, F., Bartz, H., & Puchinger, S. (2022). Error-Erasure Decoding of Linearized Reed-Solomon Codes in the Sum-Rank Metric. arXiv preprint arXiv:2202.06758.

Ray, I., M.J. Sibley, and P.J. Mather, Performance analysis of offset pulse-position modulation over an optical channel. Journal of lightwave technology, 2011. 30(3): p. 325-330.

Al-Nedawe, B.M., Microelectronic Implementation of Dicode PPM System Employing RS Codes. 2014, University of Huddersfield.

Farhat, Z.A., et al. Improved BER for offset pulse position modulation using priority decoding over VLC system. in 2019 Wireless Days (WD). 2019. IEEE.

Mahmood, F. H. (2017). Implementation of Offset Pulse Position Modulation (Doctoral dissertation, University of Huddersfield).

Hamdoon, A.M.A., Z.G. Mohammed, and E.A. Mohammed, Design and implementation of single bit error correction linear block code system based on FPGA. TELKOMNIKA Telecommunication Computing Electronics and Control, 2019. 17(4): p. 1785-1795.

Brown, S., & Vranesic, Z. (2008). EBOOK: Fundamentals of Digital Logic. McGraw Hill.

Van Helleputte, N., Verhelst, M., Dehaene, W., & Gielen, G. (2009). A reconfigurable, 130 nm CMOS 108 pJ/pulse, fully integrated IR-UWB receiver for communication and precise ranging. IEEE Journal of Solid-State Circuits, 45(1), 69-83.

Tinder, R. F. (2000). Engineering Digital Design: Revised Second Edition. Elsevier.

Ray, I., Analysis of Offset Pulse Position Modulation. 2015, University of Huddersfield.

Liu, Y. (2022, June). Design of pulse position modulation system based on programmable logic device. In International Conference on Neural Networks, Information, and Communication Engineering (NNICE) (Vol. 12258, pp. 713-720). SPIE.

Lim, C. G., & Kim, C. W. (2022). Design Methodology for Capacitively Coupled Continuous-time Delta-sigma Modulator. Journal of Integrated Circuits and Systems, 8(1).

Albatoosh, A. H., Shuja'a, M. I., & Al-Nedawe, B. M. (2022, June). Effectiveness Improvement of Offset Pulse Position Modulation System Using Reed-Solomon Codes. In 2022 International Congress on Human-Computer Interaction, Optimization and Robotic Applications (HORA) (pp. 1-5). IEEE.

Downloads

Published

How to Cite

Issue

Section

License

Copyright (c) 2022 Ahmed H. Albatoosh, Mohamed Ibrahim Shuja'a, Basman M. Al-Nedawe

This work is licensed under a Creative Commons Attribution 4.0 International License.